# Washington University in St. Louis Etching Capabilities

Nathan Reed nreed@wustl.edu

# Washington University in St. Louis School of Engineering & Applied Science

# Oxford Plasmalab System 100- ICP180

Process chamber: ICP180 for 4" wafers

Chamber heating: Yes

Lower electrode type: Clamped ICP source: ICP180 2000W

Lower electrode power supply/automatch: 600W + vacuum cap automatch

Vacuum gauges: 100mT CM gauge + Penning

Pumping pipework/APC valve: 160mm + 200mm VAT Toxic gas lines/MFCs: **20 NF<sub>3</sub>**, **100 BCl<sub>3</sub>**, **100 Cl<sub>2</sub>**

Non-toxic gas lines/MFCs: 100CF<sub>4</sub>, 100 O<sub>2</sub>, 100 CHF<sub>3</sub>, 100 Ar, 100 N<sub>2</sub>, 100 He, 100SF<sub>6</sub>

Loadlock: Single wafer

Heater/chiller: Yes 10 to 90'C

Endpoint Detectors: Integrated Laser Interferometer End Point Detector

Chamber Pumps: Aclatel 500l/s magnetic turbo pump backed by Alcatel 2063 Wet Pump

Loadlock Pumps: From Process backing

| Gas  | Application |

|------|-------------|

| CF4  |             |

| SF6  | Si          |

| CHF3 | SiO2        |

| NF3  | Si, SiC     |

| BCI3 | Al          |

| CI2  | III-V, AI   |

| HBr  | III-V       |

| Ar   | additive    |

| 02   | polymer     |

| He   | cooling     |

| CH4  | III-V       |

| H2   | III-V       |

| 755  |             |

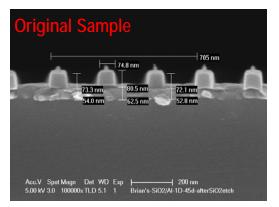

#### **Aluminum Etching**

Sample: Aluminum film (80-nm thick) on silicon wafer, masked with SiO2 patterns (75-nm lines, 70-nm thick)

Recipe: 20sccm Cl2, 5mTorr, 200W, 1000W, 10Torr He, 80C, 10sec 20sccm HBr, 2mTorr, 100W, 800W, 10Torr He, 80C, 40sec

## NANO RESEARCH FACILITY

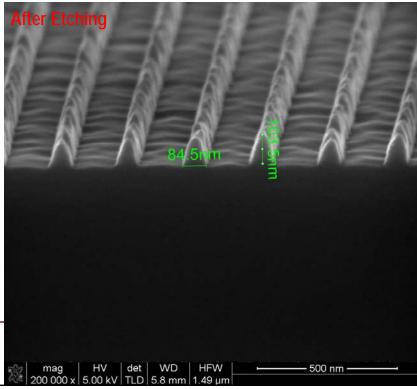

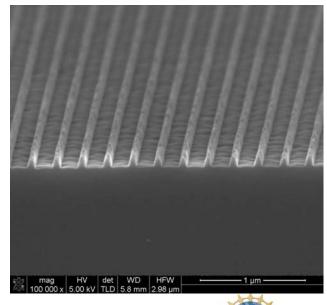

## Silicon Etching

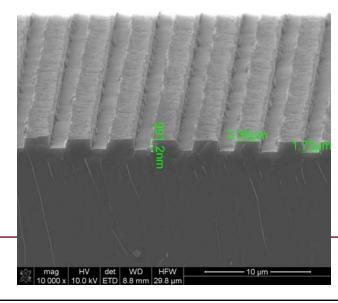

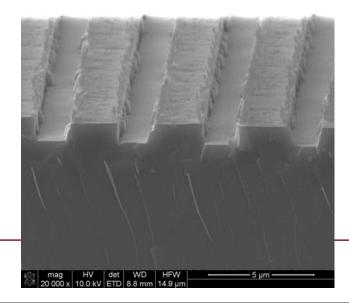

Sample: silicon wafer, masked with AZ5214 patterns (2-um lines, 10-um lines, etc.)

Recipe: 50sccm HBr, 7mTorr, 50W, 750W, 10Torr He, 50C, 5min

Note: the roughness of silicon ribbon edges was transferred from AZ patterns.

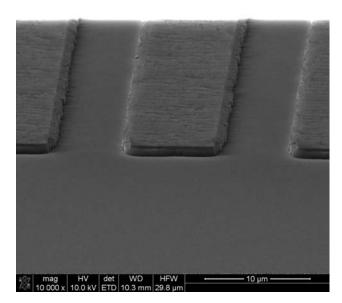

#### **GaAs Etching**

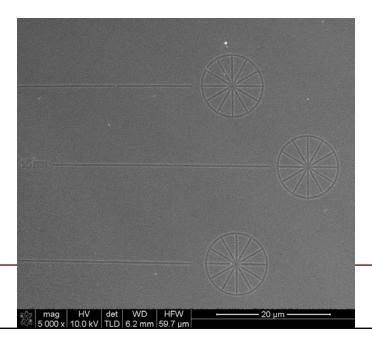

Sample: GaAs wafer, masked with PMMA patterns (e-beam lithography)

Recipe: 50sccm BrCl3, 5mTorr, 200W, 600W, 10Torr He, 10C, 30sec

30sccm BCl3, 80sccm Cl2, 7mTorr, 115W, 600W, 10mTorr He, 10C, 15sec

Etch rate: ~ 1µm/min

Selectivity to resist: ~ 5-15:1 Selectivity to oxide: ~ 15-30:1

Profile: Anisotropic

# **Chamber Conditioning**

- 15 minute O<sub>2</sub> after each run

- 1 hour clean each month

- User discretion for additional conditioning based on previous runs

#### **Future Plans**

- No new tool acquisitions

- Development of new baselines, recipes, and SOPs

- Development of new maintenance strategies

## Questions?

nano.wustl.edu nreed@wustl.edu